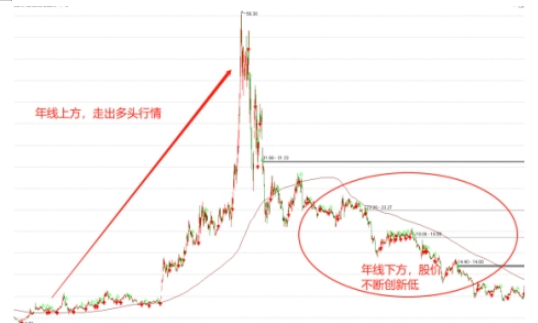

光大证券发布研究报告称,Chiplet有望成为先进制程国产替代的突破口之一。随着Chiplet小芯片技术的发展以及国产化替代进程的加速,Chiplet为国产替代开辟了新思路。

该行认为先进封装是实现Chiplet的前提,Chiplet市场规模有望从2024年的58亿美元快速增长到2035年570亿美元。

随着晶体管制程缩小技术的发展日渐困难,先进封装包括Chiplet技术成为超越摩尔定律的关键赛道。封测行业景气度有望随着23H2半导体行业复苏而回升。

光大证券主要观点如下:

先进封装成为超越摩尔定律的关键赛道。

摩尔定律(Moore’slaw)的主要内容是集成电路上可容纳的晶体管数目大约每隔两年就会增加一倍,芯片的效能也会提高一倍,但是先进制程发展到3纳米以下开始接近物理极限,短道沟效应导致的漏电、功耗严重等问题使得晶体管缩小的技术发展日渐困难,成本也愈来愈高,因此有必要利用其他手段缩小集成电路的尺寸同时降低成本。

所谓的MorethanMoore是指以系统应用的概念为出发点,不执着在晶体管的制程点缩小的摩尔定律,而更应该将各种技术进行异质整合,其中最重要的方法之一就是先进封装技术。

先进封装技术能进一步提高芯片的集成度并且降低芯片制造的成本,同时暂不涉及到去突破量子隧穿效应等物理极限问题,已经成为超越摩尔定律的关键赛道。

先进封装应用不断扩大,预计在2026年将占到整个封装市场的规模的50%以上。

先进封装技术与传统封装技术通常以是否焊线来区分:传统的封装技术通常指先将晶圆切割成单个芯片,再进行封装的工艺形式,其包括双排直立式封装DIP与球格阵列封装BGA,需要焊接线路;先进封装则包括倒装(FlipChip)、凸块(Bumping)、晶圆级封装(Wafer-level-package)、2.5D封装(interposer,RDL等)、3D封装(TSV)等封装技术,其技术并不需要用到线路焊接的方式。

倒装:带有倒装芯片结构的封装是先在芯片上制作金属凸点,然后将芯片面朝下利用焊料直接与基板互连,通常会使用底部填充(UnderFill)树脂对热应力进行再分布来提高可靠性。其优点是封装面积减小,引线互连长度缩短,I/O端口数量增加。

WLP:直接以晶片为加工对象,同时对晶片上的众多芯片进行封装及测试,最后切割成单颗产品,可以直接贴装到基板或PCB上,其中主要工艺为再布线(RDL)技术,包括溅射、光刻、电镀等工序。

WLP的优点是封装产品轻薄短小,信号传输路径更短,在生产方面可大大提高加工效率,降低成本。根据结构的不同,WLP可分为扇入型(Fan-in)和扇出型(Fan-out)两种。其中,产品尺寸和芯片尺寸在二维平面上一样大的称为扇入型,产品尺寸比芯片尺寸在二维平面上大的称为扇出型。

2.5D封装:在2D封装结构的基础上,在芯片和封装载体之间加入了一个硅中介转接层,该中介转接层上利用硅通孔(TSV)连接其上、下表面的金属,多采用倒装芯片组装工艺。由于采用了中介转接层,其表面金属层的布线可以使用与芯片表面布线相同的工艺,使产品在容量及性能上比2D结构得到巨大提升。

3D封装:是将芯片与芯片直按堆叠,可采用引线键合、倒装芯片或二者混合的组装工艺,也可采用硅通孔技术进行互连。3D结构进一步缩小了产品尺寸,提高了产品容量和性能。目前,散热较差、成本较高是制约TSV技术发展的主要因素。

先进封装被广泛应用于计算机、通信、消费类电子、医疗、航天等领域,推动着封装技术及整个电子行业向前发展。目前,倒装芯片、2.5D封装、3D封装主要用于存储器、中央处理器(CPU)、图像处理器(CPU)等;WLP主要应用于功率放大器、无线连接器件、射频收发器等。

根据Yole预测,先进封装市场预计将在2019-2025年间以6.6%的复合年增长率增长,到2025年将达到420亿美元,远高于对传统封装市场的预期;与传统封装相比,先进封装的应用正不断扩大,预计到2026先进封装将占到整个封装市场规模的50%以上。

先进封装是实现Chiplet的前提,Chiplet市场规模有望从2024年的58亿美元快速增长到2035年570亿美元。

Chiplet也称芯粒,通俗来说Chiplet模式是在摩尔定律趋缓下的半导体工艺发展方向之一,是将不同功能芯片裸片的拼搭,在某种意义上也是不同IP的拼搭,像拼接乐高积木一样用封装技术整合在一起,借此可以实现对先进制程迭代的弯道超车,在提升性能的同时实现低成本和高良率。

Chiplet对先进封装提出更高要求,在芯片小型化的设计过程中,需要添加更多I/O来与其他芯片接口,裸片尺寸有必要保持较大且留有空白空间,导致部分芯片无法拆分,芯片尺寸小型化的上限被pad(晶片的管脚)限制。

并且单个晶片上的布线密度和信号传输质量远高于Chiplet之间,要实现Chiplet的信号传输,就要求发展出高密度、大带宽布线的“先进封装技术”。

AMD、台积电、英特尔、英伟达等芯片巨头近年来纷纷布局Chiplet,AMD最新几代产品都极大受益于“SiP+Chiplet”的异构系统集成模式,近日苹果最新发布的M1Ultra芯片也通过定制的UltraFusion封装架构实现了超强的性能和功能水平,包括2.5TB/s的处理器间带宽。

据Omdia报告,预计到2024年,Chiplet市场规模将达58亿美元,2035年则超过570亿美元,将迎来快速增长。

Chiplet有望成为先进制程国产替代的突破口之一。

全球半导体产业博弈升级,国内晶圆厂在先进制程升级上受限。2022年12月《小芯片接口总线技术要求》标准发布,这是中国首个原生Chiplet技术标准,有助于行业规范化、标准化发展,为赋能集成电路产业打破先进制程限制因素,提升中国集成电路产业综合竞争力,加速产业进程发展提供指导和支持。

随着Chiplet小芯片技术的发展以及国产化替代进程的加速,在先进制程受到国外限制情况下,Chiplet为国产替代开辟了新思路,有望成为我国集成电路产业逆境中的突破口之一。

半导封测行业景气度有望随着23H2半导体行业复苏而回升。

根据22Q4财报,台积电观察到消费电子、PC、数据中心等需求不足,预计半导体周期将在23H1达到底部,23H2开始复苏;中芯国际认为23H1行业周期尚在底部,下半年虽可见度依然不高,但已感受到客户信心些许回升。

半导体封测行业22年受到行业景气度下行的影响,23年下半年景气度有望随着半导体行业复苏而回升。

风险提示:技术研发不及预期,下游应用及扩展不及预期,市场竞争加剧的风险。

来源:整理自光大证券研报

未经允许不得转载:财富在线科技 » Chiplet等先进封装应用不断扩大,行业景气度有望23H2实现回升

评论前必须登录!

登陆 注册